# 8087 Co Processors and Architechture

#### Overview

Each processor in the 80x86 family has a corresponding coprocessor with which it is compatible.

Math Coprocessor is known as NPX,NDP,FUP.

Numeric processor extension (NPX),

Numeric data processor (NDP),

Floating point unit (FUP).

#### **Compatible Processor and Coprocessor**

#### Processors

- 1.8086 & 8088

- 2.80286

- 3.80386DX

- 4.80386SX

- 5.80486DX

- 6.80486SX

#### Coprocessors

- 1.8087

- 2.80287,80287XL

- 3.80287,80387DX

- 4.80387SX

- 5. It is Inbuilt

- 6.80487SX

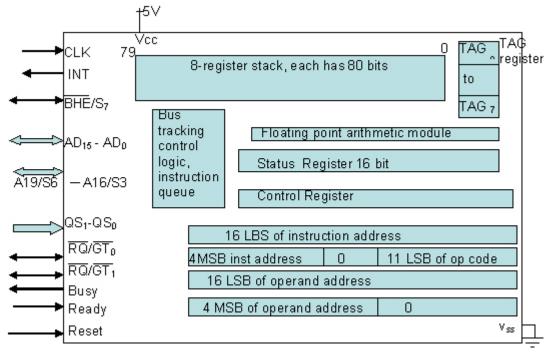

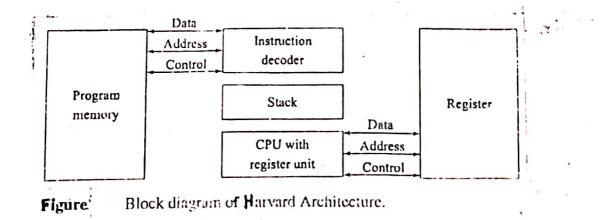

#### Architecture of 8087

□Control Unit □Execution Unit

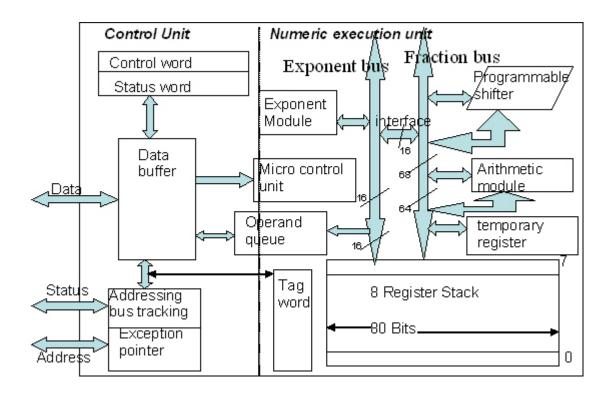

#### **Control Unit**

$\Box$  Control unit: To synchronize the operation of the coprocessor and the processor.

□ This unit has a Control word and Status word and Data Buffer

$\Box$  If instruction is an *ESC*ape (coprocessor) instruction, the coprocessor executes it, if not the microprocessor executes.

□ Status register reflects the over all operation of the coprocessor.

Architecture of 8087

#### **Status Register**

| 15 |           |    |    |    |    |    |    |    |    |    |    | 0  |  |

|----|-----------|----|----|----|----|----|----|----|----|----|----|----|--|

| B  | <b>C3</b> | ST | C2 | C1 | C0 | ES | PE | UE | OE | ZE | DE | IE |  |

- C3-C0 Condition code bits

- TOP Top-of-stack (ST)

- ES Error summary

- PE Precision error

- UE Under flow error

- OE Overflow error

- ZE Zero error

- DE Denormalized error

- IE Invalid error

- B Busy bit

□B-Busy bit indicates that coprocessor is busy executing a task. Busy can be tested by examining the status or by using the FWAIT instruction. Newer coprocessor automatically synchronize with the microprocessor, so busy flag need not be tested before performing additional coprocessor tasks.

□C3-C0 Condition code bits indicates conditions about the coprocessor.

$\Box$  TOP- Top of the stack (ST) bit indicates the current register address as the top of the stack.

□ES-Error summary bit is set if any unmasked error bit (PE, UE, OE, ZE, DE, or IE) is set. In the 8087 the error summary is also caused a coprocessor interrupt.

□PE- Precision error indicates that the result or operand executes selected precision.

UE-Under flow error indicates the result is too large to be represent with the current precision selected by the control word.

$\Box$ OE-Over flow error indicates a result that is too large to be represented. If this error is masked, the coprocessor generates infinity for an overflow error.

$\Box$ ZE-A Zero error indicates the divisor was zero while the dividend is a non-infinity or non-zero number.

DE-Denormalized error indicates at least one of the operand is denormalized.

$\Box$  IE-Invalid error indicates a stack overflow or underflow, indeterminate from (0/0,0,-0, etc) or the use of a NAN as an operand. This flag indicates error such as those produced by taking the square root of a negative number.

#### **CONTROL REGISTER**

□Control register selects precision, rounding control, infinity control.

$\Box$  It also masks an unmasks the exception bits that correspond to the rightmost Six bits of status register.

□ Instruction FLDCW is used to load the value into the control register.

#### **Control Register**

| 15 |    |   |   |   |   |  |    |    |    |    |    | 0  |

|----|----|---|---|---|---|--|----|----|----|----|----|----|

|    | IC | R | С | Р | С |  | PM | UM | OM | ZM | DM | IM |

|    |    |   |   |   |   |  |    |    |    |    |    |    |

•IC Infinity control

•RC Rounding control

•PC Precision control

•PM Precision control

•UM Underflow mask

•OM Overflow mask

•ZM Division by zero mask

•DM Denormalized operand mask

•IM Invalid operand mask

$\Box$  IC –Infinity control selects either affine or projective infinity. Affine allows positive and negative infinity, while projective assumes infinity is unsigned.

#### **INFINITY CONTROL**

0 = Projective 1 = Affine □ RC –Rounding control determines the type of rounding.

#### **ROUNDING CONTROL**

00=Round to nearest or even 01=Round down towards minus infinity 10=Round up towards plus infinity 11=Chop or truncate towards zero □PC- Precision control sets the precision of he result as define in table

#### PRECISION CONTROL

00=Single precision (short) 01=Reserved 10=Double precision (long) 11=Extended precision (temporary) Exception Masks – It Determines whether the error indicated by the exception affects the error bit in the status register. If a logic1 is placed in one of the exception control bits, corresponding status register bit is masked off.

#### **Numeric Execution Unit**

□ This performs all operations that access and manipulate the numeric data in the coprocessor"s registers.

□Numeric registers in NUE are 80 bits wide.

□NUE is able to perform arithmetic, logical and transcendental operations as well as supply a small number of mathematical constants from its on-chip ROM.

□Numeric data is routed into two parts ways a 64 bit mantissa bus and a 16 bit sign/exponent bus.

Source : http://nprcet.org/e%20content/Misc/e-Learning/IT/IV%20Sem/CS%202252-Microprocessors% 20and%20Microcontrollers.pdf

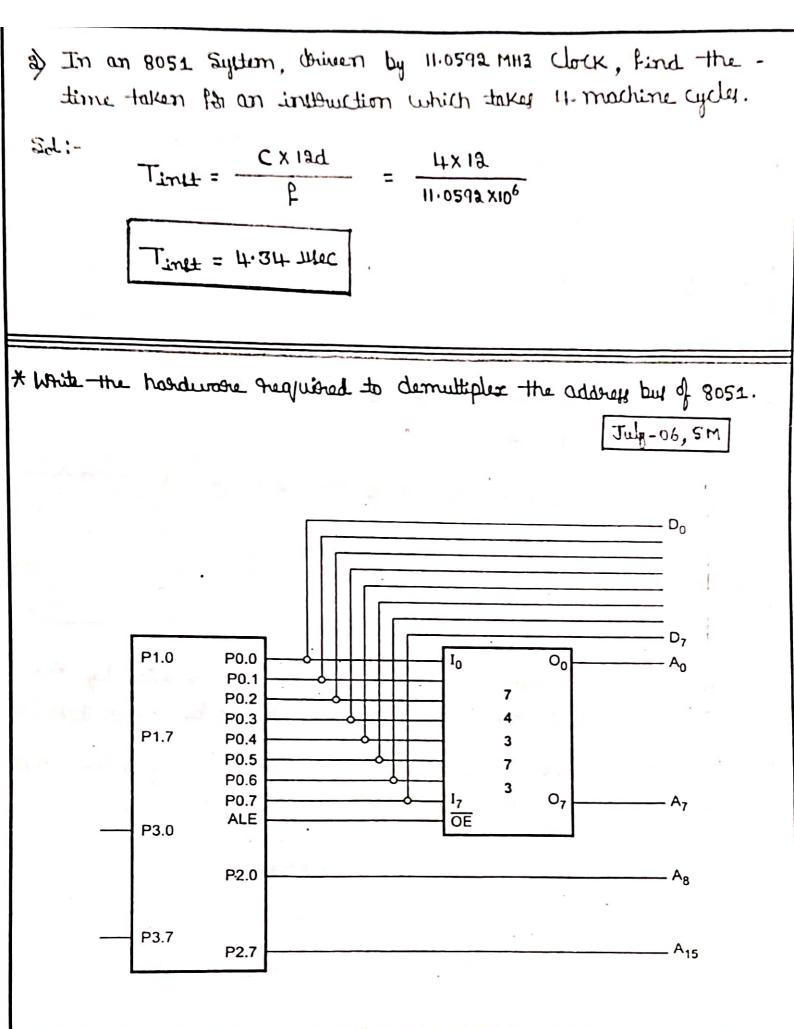

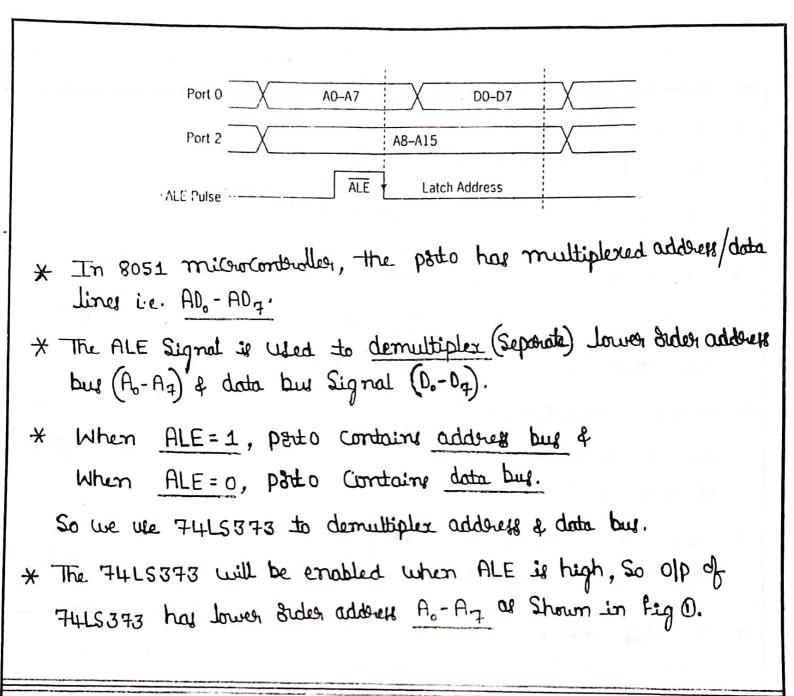

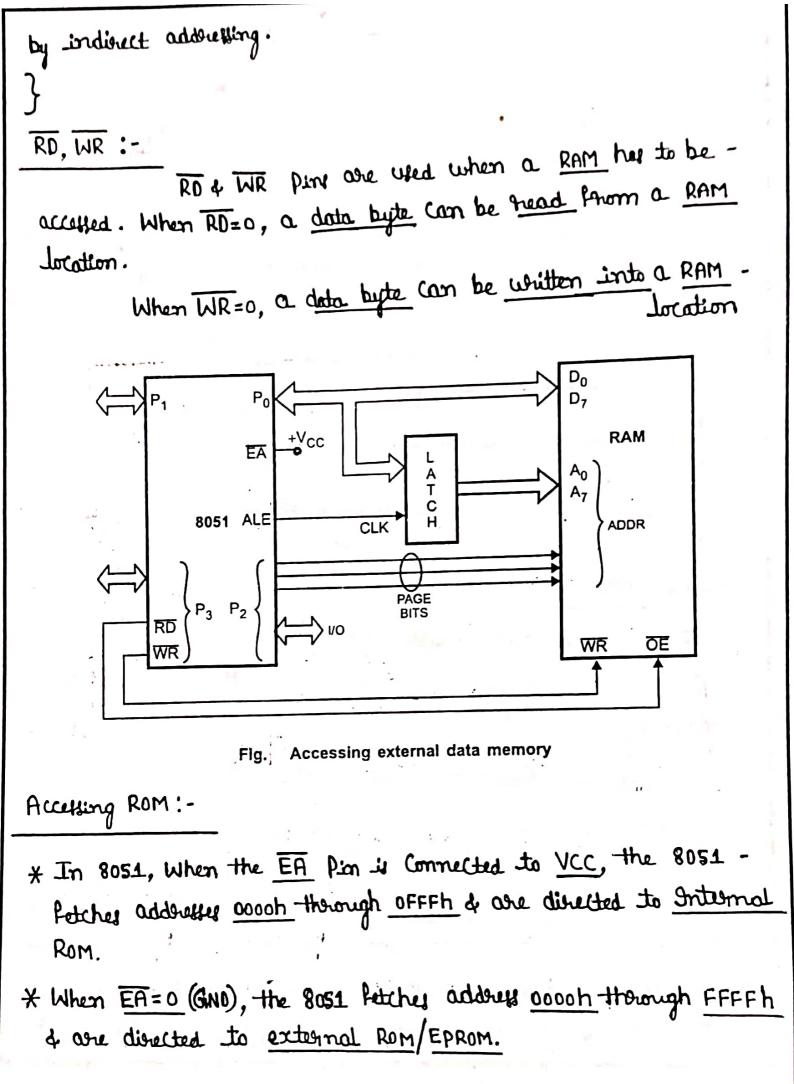

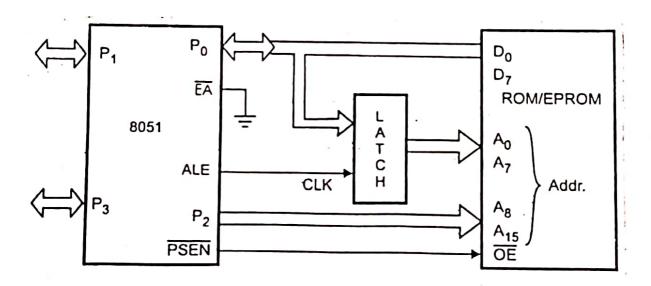

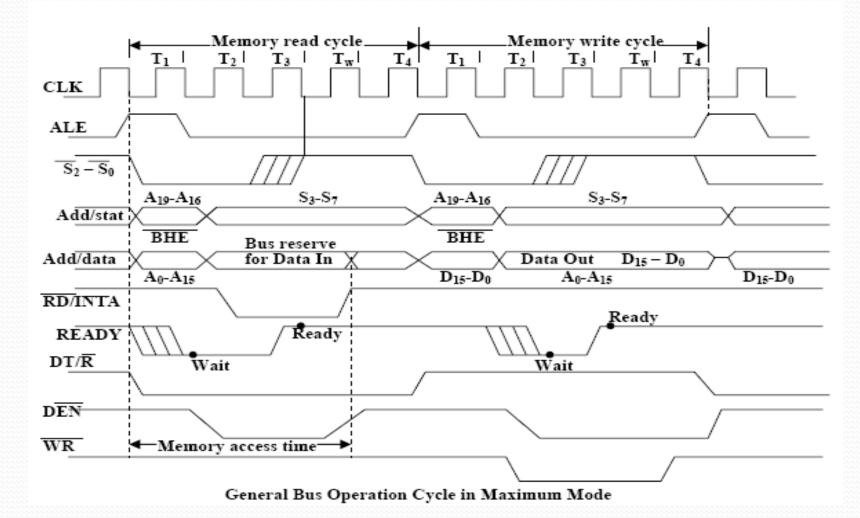

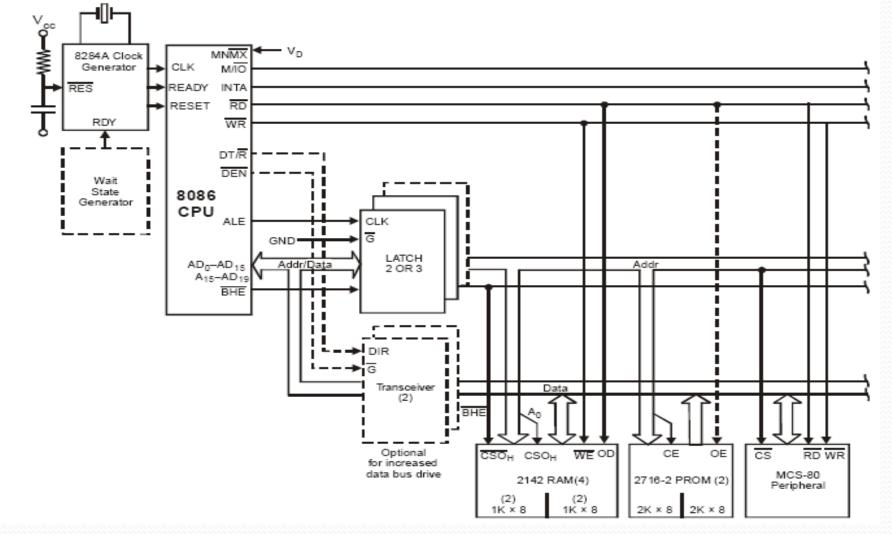

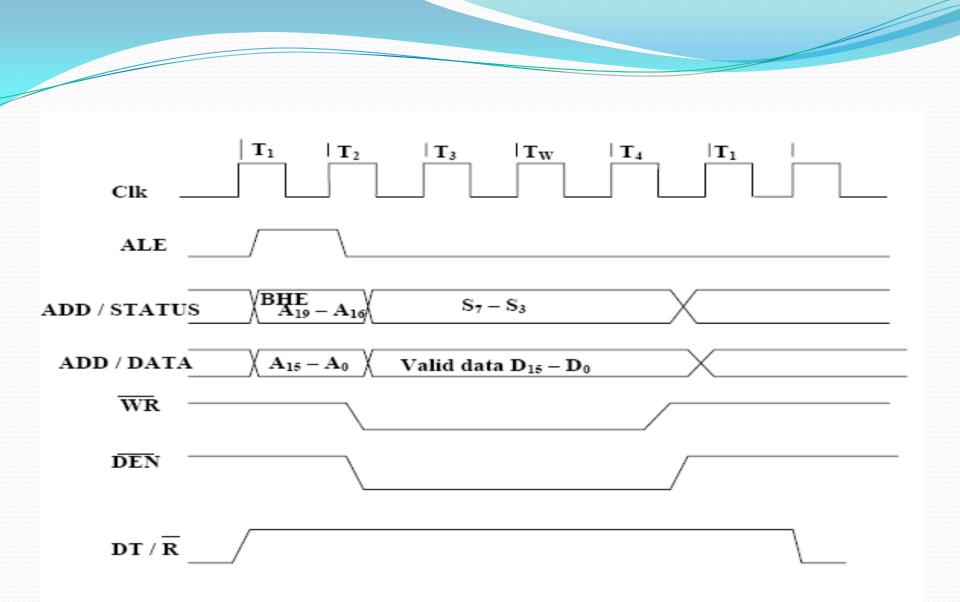

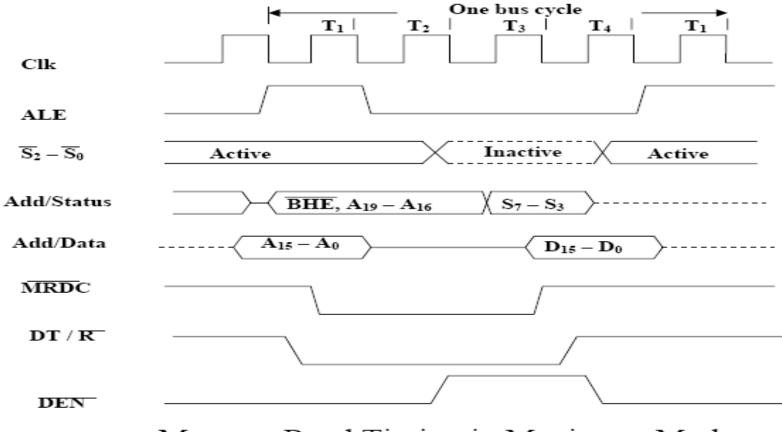

\* Difference between rainimum mode & reaximum Mode Maximum mode minimum mode

1) In minimum mode only one procession in available it's 8086

at MINIME is I to andicate min at HNAME in 0, to and wate

3) ALE for the later is given by 8086, as it is the only processor in the circuit.

the DEN and DTR for the trans-receivers are given by 8086 itself

57 Direct control Signal MIIo, RD, A WR gith by 8086

67. control signaly MITO, ROJINR are decoded by 3:8 dudder Like 74138.

7) INTA in given by 8086 in reporse to an Interrupt on INTR line.

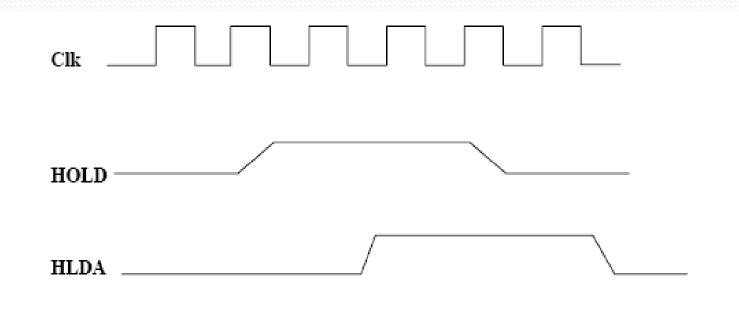

8/ HOLD & HLDA signals are used for buy request with Drift controlles like \$237

95. The circuit is simpler.

10% performance in Slower.

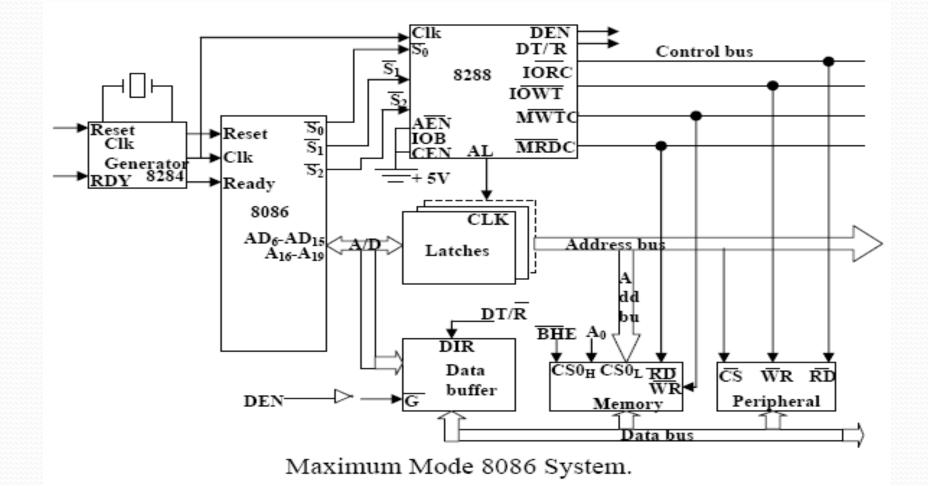

1) In maximum mode there Can be multiple proceedor with 8086 like 8087, 8089 Etc.

[0/1] may reade.

3). ALE for the latch is given by 8288, buy controller, ag there can be Multiple processo in the in wit.

4) DTIR for the trans- Tread very are given by 8288 but controller

5) Instead of control signal, Each processor generate Status Signal called 5, 52 & So

67 status signaly 51, 52 4 50 are decoded by buy controller like 8288.

7) INTA is given by buy controller 8288. in response to an Interrupt on INTR line. 8% Rug | GT lines are used for bus request by other proceeds like 8087 82 8089

97 wravit is more complex

107 performance in fatter

D. NAVEENIB Module 02: Allociate profelige Instruction Set. Dept of ECE B.G.S.I.T. Addressing modes :-\* The CPU can access data in various ways. The data could be in a seguiter, or in memory or be provided as an immediate value. \* The various ways of accessing data are called addressing moder. There are 5 addressing modes in 8051 A Immediate addressing mode. of Register addressing mode. 3) Direct addressing mode. 4> Register indirect addressing mode. Indexed addressing mode. 5) Immediate addressing mode:-. \* In this addressing mode, the source operand is a constant. The immediate data must be preceded by the pound sign "#". \* This addressing mode can be used to load injournation -n into any of the segisters, including the DPTR register & 8051 ports. ex:- 1> MOV A, #FFh. 2) MOV RA, #OAh. 3) MOV B, #10h. 4) MOV DPTR, #1234h. 5) MOV P1, #55h.

Register addressing mode:\* Register addressing mode involver the use of registers

to hold the data to be manipulated.

\* The registers A, DPTR, & Ro to Rz may be used as

Source as well as dustination.

- er:- > MOV A, RO

- 2) MOV R2,A

- 3) ADD A,R5

- A) ADD A, R7

- 5) MON RG, A

- 6) MOV DPTR, #0123h.

- 4) MOV RZ, DPL

- 8) MOV R6, DPH.

\* We can move data between the accumulator & \* We can move data between the accumulator & Rn register (n=0 to 7) but movement of data blw Rn register is not allowed.

ex:- MOV Rq, R7 18 Invalid.

31 <u>Direct</u> addressing mode :-1 1 RAM locations 00-1Fb are assigned to the segister

Janks & stack.

space to save single-bit data.

3> RAM locations 30-7th are available as a place to save byte-sized data.

\* The entire 128 byter of RAM can be accessed using direct addressing mode. The RAM locations 30h to 7Fh are most after wed.

\* In direct addressing mode, the data is in a RAM memory location whose address is known, & this address is given as a past of the instructions.

NOTE: The "#" sign distinguishes blu immediate & direct addressing.

Ex8:- 12 MOV RO, 40h. 23 MOV 56h, A 3) MOV R=, 01h. 42 PUSH OEDh. 5) POP 03h etc.

2 RAM locations o to 7 are allocated to bank o register 20-R7. Thue registers can be accused in two ways. 12 MOV A, R4 13 same as mov A,4 2) MOV A, R7 is same as mov A,7 3) MOV A, R7 is same as mov A,0. 3) MOV A, R0 10 same as mov A,0. 4) MOV Re, R3 10 same as mov 2,3 but Invalid met A) Register Indirect addressing mode :-\* In register indirect addressing mode a register is wed to hold the address of the data.

The segester itself is not the address, but sather the number in the segester.

\* The instanction for indirect addressing uses MOV opcodes along with segester Ro or Rs. Register to or Rs will hold the RAM addresses sanging from och to 4Fh.

\* The mnemonic symbol used for indirect addressing is the "at" sign i.e., "@".

Ex:- 1> MOV A, @RD.

\$ MOV @R1, B

3) MOV @RI, A

4) MOV 20h, @R1

5) MOV @ RO, 03h.

Limitatione of register indirect addressing mode:-\* Ro & Rs are the only registers that can be wed for pointers in register indirect addressing mode. Since Ro & Rs are 8-bit edde, their use is limited

5/ Indexed addressing made :-

\* Indexed addressing mode is widely used in accessing data elements of look-up table. entries located in the program ROM space.

\* The instruction's used for this purpose is 1> MOVC A, @A + DPTR

11> MOVE A, @A+PC

9) MOVE A, Q.A + DPTR : Add the contents of the accumulator with the contents of the DPTR register to form a program code memory location address. More the contents of this external memory address to the accumulator.

11> MOVE A , @A + PC :-

Add the contents of the accumulator with the contents of the pc segister to form a program code memory location address. Move the contents of this external memory address to the accumulator

Instruction Set - 8051

AMOLIAL Prof. Dept g EEE B.G.S.I.T.

Based on the operations performed, the instruction set of 8051 are classified as 1) Data transfer instructions.~ 2) Asithmetic instructions 3) Logical instructions. 1 4) Boolean instructions. 5) program branching or Machine control instructions. \* Each instruction has two pasts: <u>operation</u> <u>code</u> & <u>operande</u>. A Data Taansfer group:-The instruction in this group are MOV, PUSH, POP, XCH. (i) MOV : Mov instruction copies data pour one location to another location. Systax: - Mov operand 1, operand 2 Famat: - MOV Destination, source; copy from source to destination.

| 1) MOV A, Bn. Destination (Opran 1)                   |

|-------------------------------------------------------|

| Bytes: 1 Source je premole)                           |

| cycles: 1                                             |

| status glags affected : None.                         |

| operation: MOV                                        |

| $(A) \leftarrow (R_n)$                                |

| Description :- This instruction moves the contents of |

| Rn segister to accumulator. The Kn                    |

| regierer is not affected.                             |

| NOTE:- Rn may be Ro to Rz sugestes of the             |

| is calculad trank.                                    |

| er:- MOV A, R3 CRONT AS - 58 A 2 68                   |

| Before Execution ~> R3=58h, A= Any Value say 10h.     |

| After Execution -> A = 58h. & R3 = 58h.               |

|                                                       |

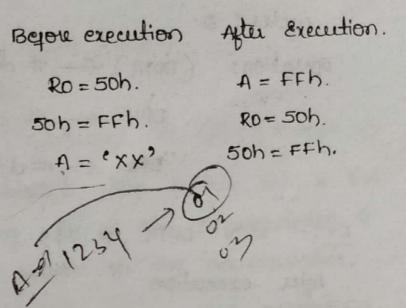

| >> MOV A, direct (Direct address)                     |

| Bytes: 2.                                             |

| cycles: 1                                             |

| operation: (A) (direct)                               |

| Description: This instruction moves the contents of   |

| the address into A segister.                          |

| Flags affected: None                                  |

100:- MOV A, 40h.

After Execution. Before Execution. A + FF At 'XX' ADH + FF ADA - FF

NOTE: -. Here 10h is a direct address. The direct address content 'FF' is moved into Accumulator.

3> MOV A, @R: only. Ri -> Register Ro or R1 Bytes: 1 cycles: 1. Ri -> Internal register. operation:  $(A) \leftarrow ((R_1))$ Description : Flags affected: None.

<u>er:-</u>

MOV A, @Ro.

Say Ro = 40h - address.

ADh = FF - data.

\* The address soh is in register Ro.

\* The data FF. 1s in address 40h.

Before execution. After execution.

Rot 40h. Ro - 40h. ADD + FF toh + FF. A & FF. A ( 'XX'

| A) MOV A, # data.                                                                                                                | and to the most most mil                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| er:- MOV A,#28                                                                                                                   | is moved into accumulator.<br>After execution.                                                  |

| Before execution $A \leftarrow 'xx'$                                                                                             | A K- 28.                                                                                        |

| 5) MOV Rn, A<br>Bytes: 1.<br>cycles: 1.<br>operation: $(R_n) \leftarrow (A)$ .<br>Description: The contents of<br>to register Rn | Romany be any Register<br>i.e. Ro-Rz ef the cuerently<br>selected bank.<br>accumulator is moved |

| Flags affected: None.<br>exs- MOV Rz, A                                                                                          | lin                                                                                             |

| Before Execution $R_7 = ' \times \times '$                                                                                       | After execution.<br>$R_3 = FF$<br>A = FF.                                                       |

A = FF

= FF. A

61 MOV Rn, Dissect Bytes: 2  $R_n$  may be any sequeter  $R_0$  to  $R_3$ ). Cijclu: 2.  $eperation: (Rn) \leftarrow (direct)$ Itaqs appected: None. ex:- MOV R1, 40h Bepose execution. Aoh = FF  $R_1 = fxx^2$  $R_1 = FF$

=> MOV Rn, # data. Bytes: 2. cycles: 1. operation: (Rn) += data. Flags affected: None

> EXE-MOV R5, #00 Before Execution  $R_5 = ' \times \times'$ By MOV direct, A Bytes: 2. cycles: 1.

operation ; (direct) +- (A)

Flags affected: None.

Rn > may be any register (Ro to R=)

After Execution.

$R_{5} = 00$ .

ex:- MOV 50h,  $R_3$ . Before execution After execution. 50h = FF $R_3 = 00$  $R_3 = 00$

Before execution. After execution. 30h = 11 50h = 0050h = 00.

```

11) MOV direct, @ Ri

Bytes: 2

cycles: 2

operation: (direct) ~ (Ri)

Jags affected: None.

```

ex:- MOV

$$\#Oh$$

, @ Ro

Bepose execution After execution

$\#Oh = 00$   $\#Oh = FF$

$R_0 = 40h$ .

$\#Oh = FF$

$\#Oh = FF$

$\#Oh = FF$

ID> MOV dérect, # data.

Byter: 3.

cycler: 2.

operation: (dérect) ← # data.

Flags affected: None.

<u>Ex:-</u> MOV 70b, # FF

Before execution. 70h = 'XX' After execution. Foh = FF

is) MOV @Ri, direct Bytes: 2. eycles: 2.  $eperation: ((Ri)) \leftarrow (direct)$ Elogs aggested: None. ex:- MOV @RI, Foh. Before execution  $R_1 = 40h$   $Aoh = * \times x^3$ Foh = FF

After execution.  $R_1 = 40h$  40h = FF70h = FF

14} MOV @ Ri, # data.

Byter: 2

cycles: 1

operation: ((Ri)) ← # data.

Flags affected: None.

ez:- MOV @ Ro, #00

After execution. Bepose execution  $R_0 = 40h.$  $R_0 = 40h.$ 10h200. Aoh = 'xx'

\* MOV dest-bit, source-bit

function: Move bit data from source bit to. destination bit.

NOTE :-

one of the operands must be the case flag; the other may be any directly addressable bit. Flags affected: casey flag.

15) Mov c, bit

Byte: 2

cycles: 1.

epcation: (c)

$$\leftarrow$$

(bit)

Flogs affected: cassy flag (cy)

ex:- 2) Mov c, P1.4

Before execution After execution

$c = 'x'$   $c = 1$

$P1.4 = 1$   $P1.4 = 1$ .

After execution.

$c = 'x'$   $c = 0$

$P0.7 = 0$ .

$P0.7 = 0$ .

Scanned by CamScanner

execction.

1

0.

= 1.

165 MOV bit, c Bytes: 2. cycles: 2. operation: (bit)  $\leftarrow$  (c) Dags affected : None. ex: - 1> MOV P1.2, C.

c = 1.

Bejose execution After execution. P1.2 = 'x' P1.2 = 1C = 1.

il MOV P3. 7, C. Before execution After execution  $p_{3.7} = (X) \qquad p_{3.7} = 0$ c = 0. CZO

Scanned by CamScanner

Authmetic Group Of Instructions :-

\* ADD A, Source.

syntax : ADD A, operand.

~ function : Add

Description: Adde the contents of source with. Accumulator contents & result is stored in accumulator.

Days affected : c, AC & OV.

NOTE: - OV is set of if there is a casey-out of bit 6 but no casey out from bit 7 or a casey out of bit 7 but no casey out from bit 6; otherwise OV = 0.

1) ADD A, Rn. where Ro = Ro to Ry. Bytes: 1. cycles: 1 operation: (A)  $\leftarrow$  (A) + (direct) A = 0214 202 Flags affected: cy, ov & Ac. AFRI = OLI ex:- 1) ADD A, R4. AZUN Bejose execution. After execution. A= '11' A = 22 R= 11. R1 = 1.1

## Pi) ADD A, RT

Before execution.  $A \ge 00$  $R_{\mp} \ge FF$ . After execution A = FF $R_7 = FF$ .

a) ADD A, direct.

Byter: 2. cyclus: 1 operation: (A) (A) + (direct) Flags affected: CY, AC, OV.

ex: - ADD A, AOh.

Before execution. After execution. A=11 A = 33 Aoh=22. Aoh=22.

```

3 ADD A, @RI

```

Bytes: 1 cycles: 1 operation:  $(A) \leftarrow (A) + ((Ri))$

Ilage affected : CY, AC, OV.

```

ex:- ADD A, @R1

```

Before execution.

$A = 30 \leftrightarrow$  RI = 70h. $70h = 20 \leftrightarrow$  Where Ra -> may be Ro or Ry.

```

Program:-

MOV @ RI, # 70h.

MOV A, # 30h

ADD A, @ RI.

```

After execution.

A = 50RI = 70h.

70h = 20.

A) ADD A, # data. Bytes : 2. cycles: 1. operation: (A) (A) + # data. Flags affected : cy, or, Ac. ex: - ADD A, # OIh. After execction. Before execution. A = 0a.A=01. 5) ADDC A, Rn. Byter : 1 cycles: 1 operation: (A)  $\leftarrow$  (A) + (C) + (en) Description: Simultaneously adds the contents of Rn sighter, the carry flag & the accumulator contents, result is stored in accumulator. Flags affected: OV, CY, AC. ex:- 1> ADDC A, RI After execution Byore execution A = 03 1 A 2 01 - C = 1 C=1)  $R_{1} = 01.$  $R_{7} = 01_{1}$

11) ADDC A, Ro

Repore execution After execution.

$$A = D1$$

,  $A = D2$

$C = 0$ ,  $T = D$

$R = D1$ .

$R = D1$ ,  $A = D2$

$C = 0$ ,  $T = D$

$R = D1$ .

$R = D1$ .

$R = D2$

$R = D1$ .

$R = D2$ .

$R = D1$ .

$R = D2$ .

$R = D1$ .

$R = D2$ .

$R = D1$ .

$R = D2$

$R = D2$ .

$R = R_1$

$R = R_2$   $R_1$

$R = R_2$   $R_2$   $R_2$

$R = R_2$   $R_1$

$R = R_2$   $R_1$

$R = R_2$   $R_3$   $R_1$

$R = R_3$   $R_1$

$R$

| Bepore execution                  | After execution.  |

|-----------------------------------|-------------------|

| A 201                             | A 203             |

| Czl                               | Cz1               |

| Roz 70h                           | Roz 70h           |

| = 0h = 01                         | 70h= 01.          |

| 8) ADDC A, # data.                | F# a von          |

| Bytes : 2                         |                   |

| cycles : 1                        |                   |

| operation: $(A) \leftarrow (A) +$ | (c) + # data.     |

| thags affected: cy, AC, OV        | doc - A           |

| Lette- ADDC A, #01h               | ngitten estation  |

| Bepose execution.                 | After execution.  |

| A=01<br>C=1                       | A = 03.<br>C = 1. |

| q} MUL AB.                        |                   |

| Function: Multiply AxI            | Β.                |

Lunction : MUL AB multiplies the unsigned eight - bit integer i.e the contents of accumulator is multiplied with the contents of acquister B. Bytes : 1. cycles : 4.

operation:

$$(A)_{3} - 0$$

$(B)_{15} - 8$   $\left\{ \left( A \right) \times (B) \right\}$

Ilags affected : c, or

ex:- mov A, #5 mov 8, #7 MUL AB

$$4 \times 5 = 35 = 23h$$

.

$A = 35 = 23h$ .

$B = 00$

Before execution. 50×A0=3200h.

> A = 50hB = A0h.

After execution.  $A = 00h \leftarrow (0-7)$  Lower byte  $B = 3ah \leftarrow (15-8)$  Higher byte

ex:- Az 100, B= 200.

-> 100x 200 = 20,000. = 4 E20h.

AXB= 4E20h.

A=20h, 8=4E

DIV AB

Function: Divide. Bytes: 1 cycles: 4. operation:  $(A)_{15-8}$   $j \leftarrow (A) j (B)$  $(B)_{7-0}$   $j \leftarrow (A) j (B)$

flage affected: CY, DY.

Description : DIV AB dividus the unsigned & bit integer

content of accumulator by the unsigned 8-bit

integer content of 8-register.

The accumulator secrives the integer part

q the quotient's sequeres the integer part

q the quotient's sequeres the integer part

q the quotient's sequeres the integer part

q the cassy & overflow flags will be cleared.

ex:- Before execution After execution.

$$A = FBh (ASI dec)$$

A = odh (13 dec) 18)  $\frac{051}{251}$

$B = 12h (18 dec)$ .  $B = 11h (13 dec)$  18)  $\frac{051}{134(8)}$

\* the quotient 13(decimal) odh is stored in

accumulator 4 the semaindus (13 decmal) 11h

is stored in B-register.

(ex:- } A = 35, B = 10  $\frac{35}{10}$   $\frac{30}{05}$

$A = 3, B = 5$   $10 \frac{35}{05}$   $\frac{30}{05}$

$A = 3h = 18 \frac{35}{10}$   $\frac{35}{151}$

$B = 12h = 18 \frac{144}{3}$

$A = 9, B = 3$

INC A

Bytes : 1.

cycles: 1.

$eperation: (A) \leftarrow (A) + 1.$

Flags affected: None.

Bepase execution.

A201

After execution. A = 02.

12> INC RD.

Bytes : 1.

cycles: 1.

operation:  $(Rn) \leftarrow (Rn) + 1$ .

Ilags affected: Mone.

ex: INIC RO.

Beyore execution. After execution. Ro=30h. Ro=31h.

13) INC dérect

Byter: 2

cycler: 1

operation: (direct) ← (direct) + 1

Flags affected: None.

ex:- INC 40h.

Bepere execution. 40h = .01

After execution. 40h= 02.

14> INC @ RE

Byter: 1. cycles: 1. operation: ((Ri)) ← ((Ri)) + 1. Elags: None. Function: Increment.

CK: INC @ RO.

Beyore execution. Rozsoh. 80hz01. After execution.

Rozsoh

15) INC DPTR.

Function: Increment data pointer.

Byter: 1.

cycler: 2.

operation: (DPTR) ← (DPTR) + 1.

Description: This instruction increments the 16-bit register content (DPTR) by 1. This is the.

only 16-bit register that can be incremented

Flage : None.

- CK: INC DPTR.

- i) before execution.

DPTR = 16 FFh .

Begole Execution.

DDTR = OOFFh.

DPH = Ooh.

DPE = FFh.

vo t

16> DEC A.

Function: Decrement Byte: 1. cycle: 1. operation: (A) (A) - 1. Flags: None. Before execution. Az 05h. i) After execution. DPTR = 1700h. (DPH = 17, DPL = 00)

BAfter execution. DPTR = 0100h. DPH = 01h DPL = 00h.

After execution. A=04h.

14) DEC RN.

Bytu:1.

eycles:1.

operation: (ln) ← (ln) - 1.

Flags: None.

ex:- DEC RO.

Bepore execution.  $R_0 = 80h.$ 80h = 05h.

After execution. Ro = 80h. 80h=04h.

52

18> DEC direct

Byter: 2. ajcles :- 1. operation: (direct) ~ (direct) - 1.

flags: None.

ex:- DEC ADh.

40h = 05h.

Bepore execution After execution. 10h = 04h.

19> DEC @ R:

Bytes: 1.

cycles : 1.

operation:  $((R_i)) \leftarrow ((R_i)) - 1$

Flags: None.

CX:- DEC @ RO.

```

Before execution.

Ro=soh

80h=04h.

```

After execution lo=soh 80h = 03h.

DA Astrielen

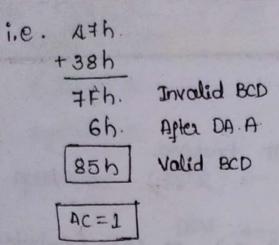

20) DA A

Function : Decimal - adjust accumulator after addition. Flags : CY.

Deuription: This instruction is med after addition of BCD numbers to convert the secult back to BCD. The data is adjusted in. the following two possible cases.

1) It adde 6 to the lower A-bilt of A y it is greater than 9 or if AC=1.

2) It also adds & to the upper 4-bits of A y it is qualter than 9 or if CY=1.

Byter : 1.

cycles : i.

operation:  $1p \left[ \left[ (A_{3-0}) > 9 \right] \vee \left[ (Ac) = 1 \right] \text{ Then} \right] (A_{3-0}) \leftarrow (A_{3-0}) + 6.$

$$If [[(A_{3-4}) > 9] \vee [(c) = 1]] \cdot Then.$$

$$(A_{3-4}) \leftarrow (A_{3-4}) + 6.$$

ex:- MOV A, #47h. A=47h. ADD A, #38h ; A=47h+38h=7Fh, invalid BCD. DA A ; A=85h, Valid BCD.

\* Since the lower nibble is greater than 9, DA added 6 to A. If the lower nibble is less than 9 but AC=1, it also adde 6 to the lower nibble.

11) MOV A, # Q9h.

ADD A, # 18h.

$$\frac{+18h}{41h} + (Incorrect result in BCD)$$

DA A

$\boxed{AC=1}$

$\frac{+6}{47h} + (correct result in BCD)$

ii) MOV A, #52h.

ADD A, #91h.

DA A

$$I \to I \to I$$

$I \to I \to I$

$I \to$

AC=1, CY=1

| all subb A, source byte.                                        | 0.20 |

|-----------------------------------------------------------------|------|

| Function: subtract with boseco.                                 | O'A. |

| flage: ov, Ac, CY.                                              |      |

| operation: $(A) = (A) - (byte) - (c)$ or $(A) = (A - byte - c)$ |      |

| Description : SUBB subtracte the source byte & the              |      |

| cassey flag from the accumulator &                              |      |

| puts the sesult in the accumulator.                             |      |

| SUBB instruction sets the carry flag according                  |      |

| to the following.                                               |      |

| 1) destination > source o the assult is the.<br>byte byte.      |      |

| byte : byte.                                                    |      |

| ii) destination = source 0 the result is 0.                     |      |

| byte. byte.                                                     |      |

| iii) destination < source 1 the sesuel is -ve                   |      |

| byte byte. In a's compliment.                                   |      |

| ert:- xch A, Rn.                                                |      |

| Bytes: 1                                                        |      |

| cycles : 1.                                                     |      |

| operation: (A) $\leftrightarrow$ (Rn).                          |      |

| Flage: None.                                                    |      |

| ex:- xcH A, Ra.<br>Before execution. After execution.           |      |

| Before execution. After execution.<br>A = FFh. $A = 11h$ .      |      |

| $R_2 = 11h$ . $R_2 = Ffh$ .                                     |      |

Scanned by CamScanner

-

0. 50 ex: - MOV A, #FFh 26 MOV Ra, #11h. XCH A, Ra. XCH A, direct 23> Bytes : 2 cycles: 1 operation: (A) + (direct) Flags : None Ex:- XCH A, ADh. Bepose execution. . After execution. Arlih. A=FFh. 40h=Ffh Aoh=11h. 24> XCH A, @Ra Bytes : 1 cycles: 1 operation:  $(A) \leftrightarrow ((R_i))$ Flags : None EI:- XCH A, @R MOV 40h, #11h Before execution After execution. MOV RI, #40h. 40h = FFh. 40h = 11h.MOV A, #FFh. A = 11h. A = FFh.XCH A, @R1.

(a5) XCHD A, @R: 84.66

Function : Exchange Digit Description: The XCHD instruction exchanger only the lower nubble of accumulator (bit 3-0), with the lower mibble of the RAM location pointed to by R.

The higher - order nibbles (bits 7-4) × of each registers are not affected.

Flags : None.

Bytes : 1.

cycles: 1.

operation :  $A_{(3-0)} \leftrightarrow ((R_{3-0}))$

EX:- XCHD A, @ RJ

MOV A, # Ffh. MOV RI, # 50h. MOV 50h, # 00h. XCHD A, @RL.

Bepore execution. After execution. A=FFh. R1= 50h. 50h= 00h.

A= Foh. R1= 50h. Joh= OFh.

26} MOV DPTR, #16-bit value. Function: Load Data pointer with a 16-bit constant. Description: The data pointer 11 loaded with the 16-bit constant indicated. The DPH register bolde high-order byte, while DPL holds the Loco-order byte.

tlags: None bytes: 3 ycles: 2 operation:  $(DPTR) \leftarrow \# data (0-15)$   $DPH \leftarrow \# data _{15-8}$  $DPL \leftarrow \# data_{\mp -0}$

EX: - MOV DPTR , # 1234.

After execution DPH = 12h.DPL = 34h.

27> MOVX dest-byte; source-byte.

Junction: Move External.

- Description: \* This instruction transfers data blu external memory & register A, hence the "x" appended to MOV.

- \* The address of external memory location being accessed can be 16-bit or s-bit.

MOVX A, @R: Bytel: 1. cyclel: 2 Operation:  $(A) \leftarrow ((Ri))$ . Flags: None. Ex:- MOVX A, @ Ro.

MOV Ro, #50h. MOV 50h, #FFh MOVX A, @RO.

28} MOV A, @ DPTR. Bytes: 1. cycles: 2 operation: (A) ← ((DPTR))

Flage : None.

Ex:- MOVXA, @ DPTR.

MOV DPTR, #1234Before executionAfter execution.MOV 1234h, #FFh.1234h = FFh.A = FFh.MOV 1234h, #FFh.DPTR = 1234.DPTR = 1234h.MOVX A, @ DPTR.A = 'XX' $R34h \in FFh.$

29} MOVX @Ri, A Flags: None Bytes: 1 eycles: 2 operation:  $((Ri)) \leftarrow (A)$  EX:- MOVX @RI, A

MOV RI, # 80h. MOV RI, # 80h. MOV 80h, # AAH. MOV 80h, # AAH. MOV (0, 1, 4) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5) (1, 1, 5)(1, 1, 5)

Ex: - MOVX @ DPTR, A.

MOV DPTR, # 1234Before executionAfter execution.MOV DPTR, # 1234DPTR  $\leftarrow$  1234hA = FFh.MOV 1234, #FFh.DPTR  $\leftarrow$  1234hA = FFh.MOVX @DPTR, AI234h  $\leftarrow$  FFh.DPTR = 1234h.A  $\leftarrow$  'xx'I234 = FFh.

/Logical Instructions :-\* ANK dest-byte, Suc-byte. Function: Logical - AND for byte. variables. Description: ANL performs the betweene logical - AND operation b/w the variables indicated & stores the secult in the declination variable. A AND B. Flage : None. B A And Operation A, #02 0 0 1=02 ANL A, Rn. 41  $R_1 = 0.4$ ( Bytes : 1. 4 = 08 ~ cycles: 1. operation:  $(A) \leftarrow (A) \land (R)$ function: Logical AND for byte vasiables. Flags: None. ex: - ANL A, R5. After execution Before execution 0011 10014 39 A = 39A = 09 0000 10014 09 R5 = 09. R5 = 09 0000 1001. 09

ANL A, direct

2>

3>

eytes: 1 eycles: 1. operation:  $(A) \leftarrow (A) \land (direct)$ Flags: None.

Bepore execution A=39 Agter Execution.

| A=39     | A=09     | 39   | 100111001  |

|----------|----------|------|------------|

| 40h = 09 | 40h = 09 | N 09 | 0000 1001. |

| EQUIDE   |          | 09   | 0000 1001. |

ANL A, @Ri

RI -> RO OL RI

Bytes: 1. cycles: 1. operation:  $(A) \leftarrow (A) \land ((R_1))$ Flags: None.

| Bepore execution. | After crecel | ion.   |           |

|-------------------|--------------|--------|-----------|

| A = 39            | A=09         | A=39   | 00111001  |

| Ro = 80h.         | R0 = 80h.    | 80h=09 | 00001001  |

| 80h = 09.         | 80h=09.      | 09.    | 00001001. |

1 monal

4) ANL A, # data. Byte: 2. eycle: 1 operation: (A)  $\leftarrow$  (A) A # data. Flags: None. ex:-ANL A, # 09h. Begone execution. After execution. A = 39 A = 09.

|   | 0011 | 1001  |

|---|------|-------|

|   |      | 1001. |

| ] | 0000 | 1001  |

39

109

09

5) ANL direct, A Byte: 2 cycles: 1. operation: (Direct)  $\leftarrow$  (Direct)  $\land$  (A) Flags: None

ex:

$\begin{array}{rcl} \underline{CX:} & \underline{ANL} & \underline{40h, A} & & \underline{Ayter} & \underline{execution.} \\ & \underline{A0h} = 39 & & \underline{A0h} = \\ & \underline{A} = 09 & & \underline{A0h} = \\ & & \underline{A} = . \end{array}$

| -   |                 | and the second | ( there is a second sec |

|-----|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANL | PI,#1111110 8;  | Mask           | P1.0 (1.e Do et port1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ANL | PI,#0111111 B;  | mark           | P1.7 (1.e D7 e4 poet 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ANL | PI,#11110111 B; | Mask           | P1.3 (1.e D3 of port 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ANL | PI,#1111100 B;  | Mark           | P1.0 & P1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

\* ANL C, Source-bit

Function : Logical AND for bet variables.

Flag: cy.

Description: In this instruction carey flag bet is ANDed with a source bet & the result is placed in carry flag.

ie if source bet =0, then cy=0 otherwise cy=1.

6) ANL C, bit Bytes: 2 cycles: 2 operation: (c)  $\leftarrow$  (c)  $\land$  (bit) Flags: CY.

ez's: -

1) ANL C, ACC.7

Bepose execution. After execution

| CZI    | C=0   | $A_{2}13 = 00010011.$ |

|--------|-------|-----------------------|

| A= 13. | A=13. | Cz1 = 1               |

| H-13.  |       |                       |

lis ANL C, P2.2.

Bejore execution.

After execution.

c=1.  $P_{2} = 00001011 B.$   $P_{2} = 0Bh.$  c=1 Ruult c=0 Ruult c=0

Scanned by CamScanner

Result . C = 00010

\* ANL C, Source-bit

Function : Logical AND for bet variables.

flag: cy.

Description: In this instruction casey flag bet is ANDed with a source bet & the seculis placed in casey flag.

ie if source bit = 0, then cy=0 otherwise

6) ANK C, bit Bytes: 2 cycles: 2 operation: (c)  $\leftarrow$  (c)  $\land$  (bit) Flogs: CY.

ez's:-

1) ANL C, ACC.7

Before execution.

Before execution. After execution C=1 C=0 A=13 = 00010011. A=13. C=1 C=1 = 1A=13. C=1 = 1

lesult . c = 00010011.

Is ANL C, P2.2.

After execution.

c=1.  $P_{2} = 000010111 B.$   $P_{2} = 0Bh.$  c=1 C=0 Ruult c=0 Ruult c=0

FLAG: CY.

Ex:- 1/ ANL C, 1ACC. F

NOTE: - 1/bit → means Invest

the bit data

the bit data

(NOT)

the bit data

(NOT)

the bit data

(NOT)

the bit data

(NOT)

the bit data

(Complement)

Ex:- 1/ ANL C, 1ACC. F

Bepore execution Agta execution Acc. = 0 [111] C=1 C=1 IAcc. = 0 [11] Acc = 0 [11] Acc = 0 [11] Acc = 7Fh. IAcc. = 1 Acc = 7Fh. Acc = 1 Acc = 7Fh. Acc = 1 Acc = 1C = 1

$$31$$

ANL C, IP2.0.

Beque execution

After execution.

$c=1$ .

$C=1$ .

$P2 = 00010000$  B.

$P2 = 10h$ .

$GL$

$P3.0 = 00010000$

$P2 = 10h$ .

$IP2.0 = 00010000$

IP2.0 = 00010000

IP2.0 = 00010000

IP2.0 = 00010000

IP2.0 = 00010000

C=1

Result-

C

Scanned by CamScanner

SUNT - 0011 8) SWAP A 0010 0001 Bytu: L operation:  $(A_{3-0}) \leftrightarrow (A_{3-4})$  0001 0011 Function: swap nibbles within the accumulator. Flags: None Description: The swap instruction interchanges the lower nibble (A0-A3) with the upper nibble (A4-A7) merde register A.

ext- MOV A, #59H SWAP A Beypic execution

A= 594.

After execution. A = 95ie A = 10010101 Logical OR for the byte vasiables :-

ORL & dest-byte>, < sac-byte> or

ORL dest-byte, source-byte.

Function : Logical OR por byte variables.

Description: ORL peycame the bitudise logical-OR operation between the indicated variables, storing the results in the destination byte.

( The ORL instruction can be used to set certain bits of an operand to 1).

1) ORL A, Rn.

Bytes: 1

cycles: 1

```

operation: (A) (A) V(Rn)

```

Flage: None

Description: This instruction performs a logical OR on the byte operande, bit by bit, and stores the secult in the destination. <u>er:-orl A, R5</u> mov A, # 32h Bepore execution. After execution. A=00110010 mov R4, # 50h A= 32h A=72h R5=01010000 ORL A, R4 R5= 50h R5=50h. A<01110010

72h

Scanned by CamScanner

a) ORL A, direct

Bytes: 2

eycles: 1.

operation: (A) (A) V (direct)

Flags: None

EX:- ORL A, 30h.

Bejoie execution. After execution ie. mov A, # 32h. Az Jah. A=32h. mov 30h,# 50h. 30h = 50h.30h = 50h. ORL A, 30h.

A = 3ah.

R1=30h

30h = 50h.

3) ORL A, @Ri

Bytes: 1

cycles: 1

operation:  $(A) \leftarrow (A) \lor ((Ri))$

Flags: None

ex:- ORL A, @RI

MOV 30h, #50h. mov RI, # 30h MOV A, # 32h.

ORLA, @ RI

4)

ORL A, # data. Bytes: 2 cycles: 1 operation: (A) (A) V # data

la -> Ro & R, only.

After execution Bejoie execution

A=72h. R1 = 30h.30h = 50h.

flags: None. ext- ORL A, #50h. Bepare execution. Après execution. A = 72h.A = 32h.data = 50h. 5) ORL direct, A Bytes : 2 cycles: 1. operation: (direct) (direct) V (A) flags : None ex: DRL 30h, A. Before execution after execution. MOV A, # 32h A=72h. A = 32hmov 80h, #50h 30h = 50h. 30h = 50h.ORL 30h, A 6) ORL direct, # data. Bytes: 3. cycles: 2. operation: (direct) ~ (direct) V # data Flags: None ex: - ORL 30h, # 32h. Before execution. After execution mov 30h, # 50h 30h = 72h. 30h = 50h ORL 30h, # 32h. data = 32h.

#) ORL C, Source - bit

Function: Logical OR for bit variables.

- Description: The carry flag bit is Oked. with a source bit and the secult is placed in the carry flag.

- . If the source bit is 1, cy is set; Otherwise, the cy flag remains unchanged

- flags : cy

- \* ORL C, bit Bytes : 2 cycles : 2 operation : (c)  $\leftarrow$  (c) V (bit). Flags : CY

ex: - ORL C, ACC. 3

- i) Before execution.

- AzFF.

- 1.e A = 1110111

- 11) Before Execution A = F7

CY = 0

After execution. A = F7 CY 20

After execution.

AEFF

cy = 1

A = 11110111

| 8) ORL C, /bit<br>eytu: 2<br>cyclu: 2<br>operation: (c) $\leftarrow$ (c) V (bit)<br>Flage: CY | 1bit → NOT eg bit er bit             |

|-----------------------------------------------------------------------------------------------|--------------------------------------|

| ex:- ORL C, 1ACC.3                                                                            | Production of the second             |

| >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>                                                        | After execution.                     |

| A=00011000 b.                                                                                 | CY=D                                 |

| ie Az 18h.                                                                                    | A= 00010000 bit3                     |

| CY = 0                                                                                        | +CY = +0                             |

| r ( 442).                                                                                     | Result CY 0                          |

| 1) Before execution.                                                                          | After execution                      |

| A=00010000b                                                                                   | A = 00011000 bit 3                   |

| ie A=10h                                                                                      | cy = +0.                             |

| CYZO                                                                                          | cy =                                 |

|                                                                                               | CYZI                                 |

| and the second states the second states                                                       | A DEPARTURE AS A SULLEY AND A SULLEY |

|                                                                                               | and man and man in the               |

|                                                                                               |                                      |

|                                                                                               |                                      |

|                                                                                               |                                      |

|                                                                                               |                                      |

LOGICAL XOR :-.

XRL dest-byte, source-byte

Function: Logical exclusive - OR for byte variables. I flags: None

33

Description: performe the bitwise logical Exclusive-DR operation blue the indicated variables, storing the results in the destination.

1) XRL A, Rn Bytes: 1 eyclus: 1  $operation: (A) \leftarrow (A) \forall (ln)$ Flage: None  $\forall \rightarrow \chi OR$   $Rn \rightarrow Ro to R_7$   $A \quad B \quad A \times ORB$   $0 \quad 0 \quad 0$   $1 \quad 1$   $1 \quad 0 \quad 1$  $1 \quad 0 \quad 1$

Ex: - XRL A, R3.

mov A, # 39hBefore execution.After execution.mov R3, #09hA = 39h.0011001 = AA = 30hxRL A, R3R3 = 09h.00001001 = RR3 = 09h.volumeR3 = 09h.00001001 = RR3 = 09h.

$$2$$

xRL A, désect.

Bytes: 2

eycles: 1

operation: (A) ← (A)  $\forall$  (direct)

Flags: None

| mov A,#39h    | Bepore execution. | After execution. |

|---------------|-------------------|------------------|

| mov soh, #ogh | A = 39h.          | A= 30h.          |

| XRL A, 30h.   | 30h = 09h.        | 30hz 09h.        |

| A=39         | r | 0011 | 1001  |

|--------------|---|------|-------|

| 8<br>30hz 09 | H | 0000 | 1001. |

| A = 30       | 1 | 0011 | 0000  |

3) XRL A, @Ri

RE -> RI DL R2

Bytes: 1 cycles: 1 operation:  $(A)' \leftarrow (A) \forall ((Ri))$ Frags: None

EX:- XRL A, @ R1 MOV A, # 39h. MOV R1, # 50h MOV 50h, #09h. XRL A, @ R1.

Before execution. A = 39h R1 = 50h50h = 09h

A} XRL A, #data. Bytes: 2 cycles: 1 operation: (A) ← (A) ¥ #data Elage: None After execution.

A = 30h

Ex: - XRL A, # 09h.

mov A, # 39h  $x_{RLA}$ , # 09h. Before execution. After execution. A = 39h. A = 30h. data = 09h.

5} XRL direct, A Bytes: 2 ayeles: 1 operation: (direct) ← (direct) ¥ (A) Frags: None Ex:- XRL 50h, A

mov A, # 39hBefore execution.After execution.mov 50h, #09h.A = 39hA = 30hXRL 50h, A50h = 09h.

6≥ XRL direct, # data.

Bytes: 3.

updes: 2.

operation: (direct) ← (direct) ∀ # data

Flags: None.

Ex:- XRL 50h, #09h.

mov 50h, #39h. Before execution

XRL 50h, #09h. 50h = 39h.

data = 09h.

After execution.

50h=30h.

XRL 15 used to check whether the two register have some value. If the value is some then '0' 15 placed in accumulator of location (dufination).

## ROTATE Instructions :-

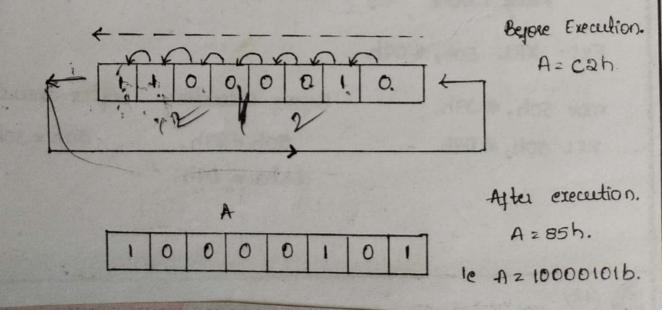

1> RL A.

TE :-

Function: lotate Accumulator left.

Description: The eight bits in the accumulator are

rotated one-bit to the left.

Bit-7 is subtated into the bit-0 position. Flags: None

Bytes: 1.

cycles : 1.

operation:  $(A_{n+1}) \leftarrow (A_n)$  where  $n \ge 0-6$ . Not (A\_0) \leftarrow (A\_4). Leas

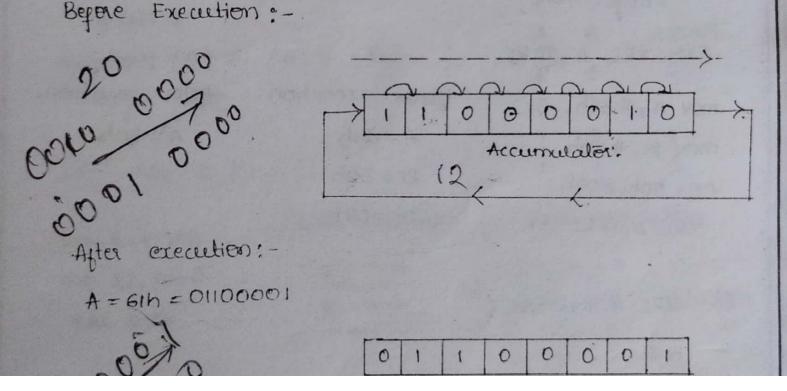

## 2) RRA.

Function: Rotate Accumulator Right

- Bytes: 1:

- cycles : 1

- Flage : None

- Description: The right bits in the accumulator are sotated one bit to the sight. Bit -0 is rotated into the bit-7 position.

- operation: (An) (An+1), n=0-6  $(A_1) \leftarrow (A_0)$

Bepere Execution :-.

Scanned by CamScanner

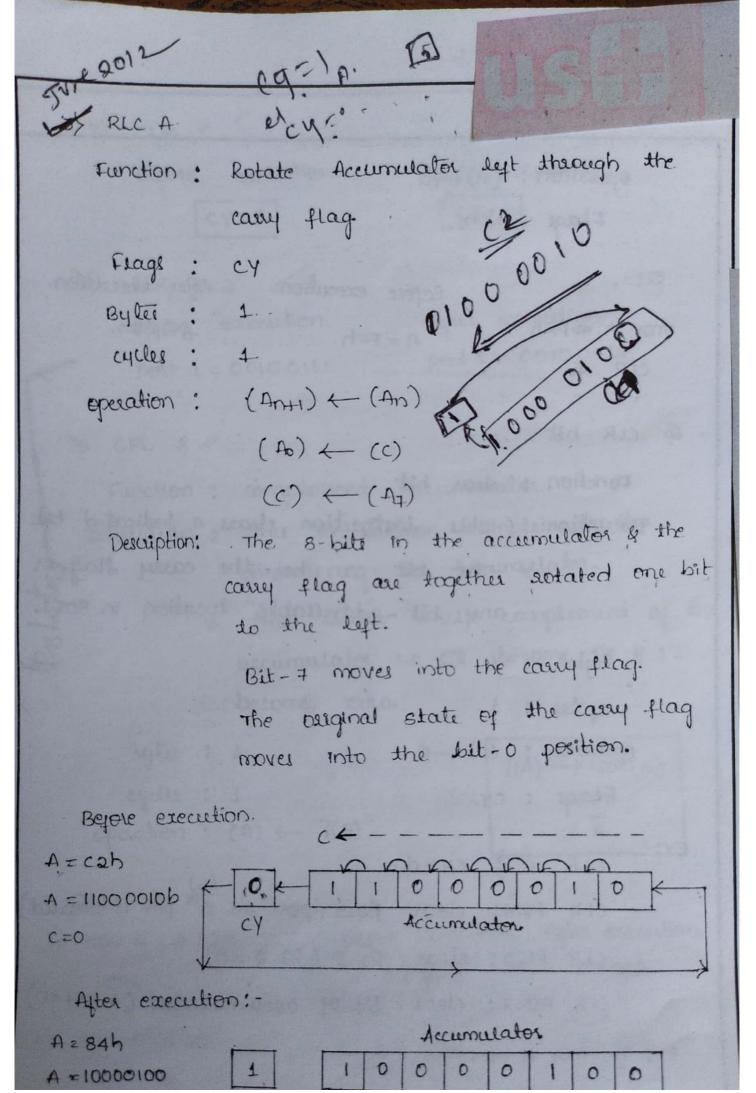

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4) RRCA P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Function : Rotale accumulator Right through the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| cassy flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| lyte : 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| cycles : 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| operation: (An) <- (An+1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $(A) \leftarrow (C)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $(c) \leftarrow (A_0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Flags: CY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |